Disseny Digital Bàsic

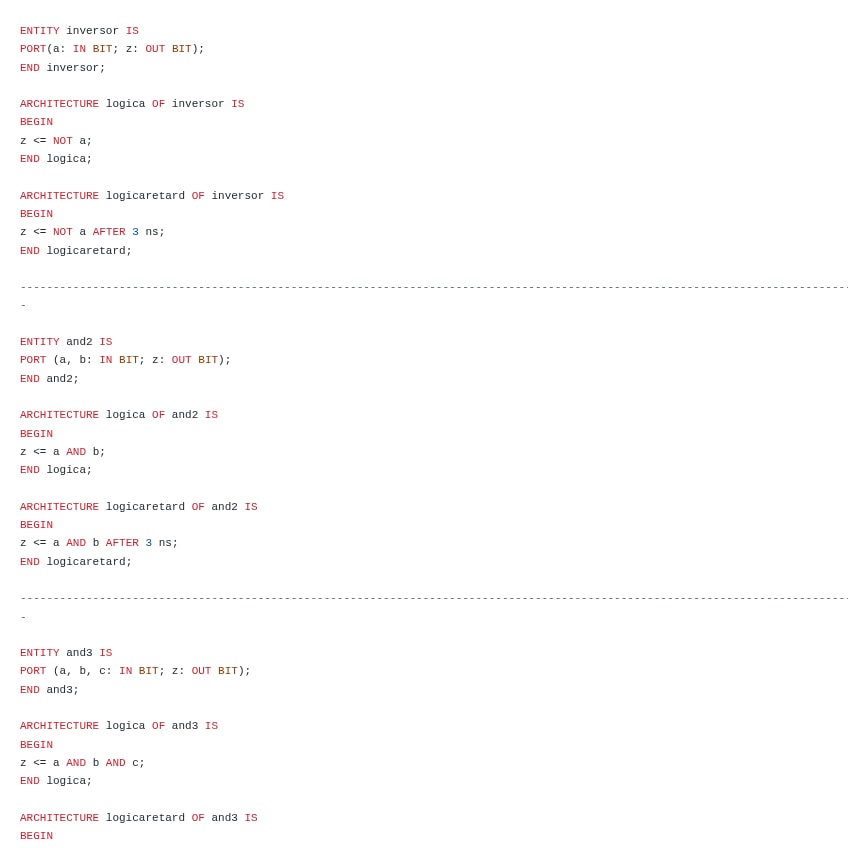

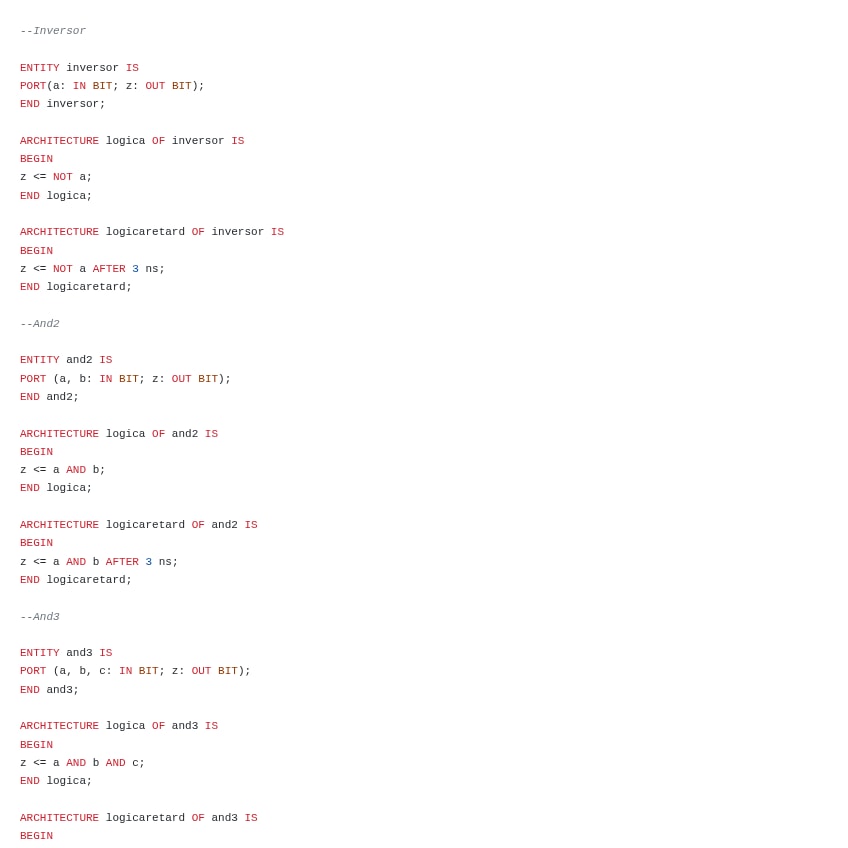

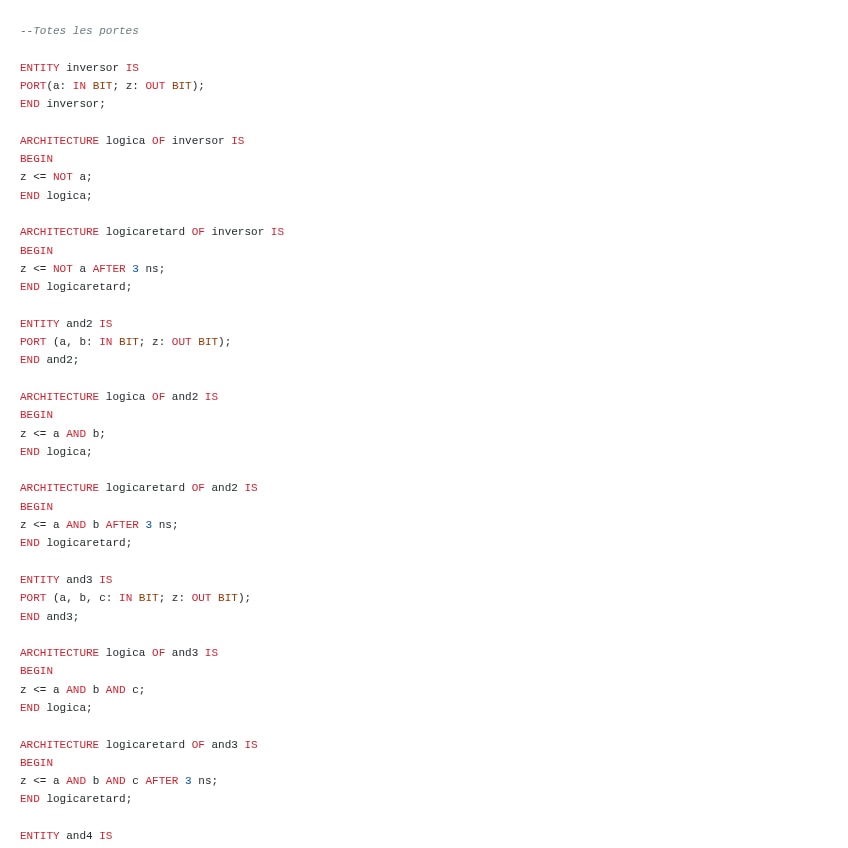

"Archivo auxiliar necesario para las prácticas de diseño estructural. Contiene la definición compilable de todas las puertas básicas (AND2, AND3, AND4, OR2, OR3, OR4, XOR2, INV) con sus arquitecturas lógica y con retardo. Úsalo como 'package' para tus eje

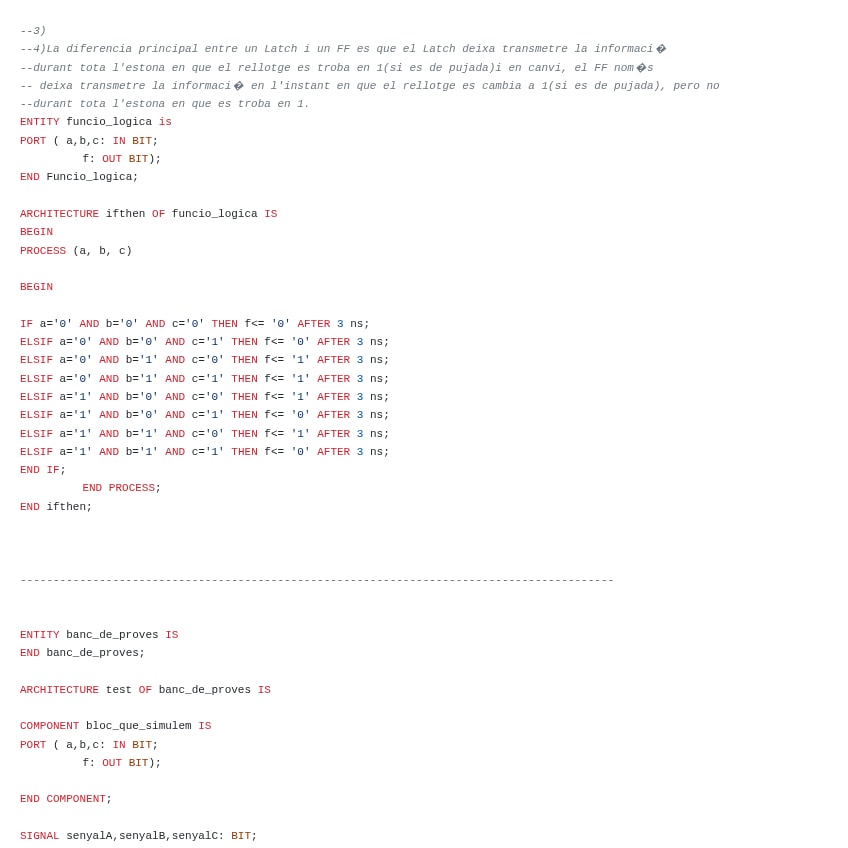

"Práctica fundamental sobre elementos de memoria. Teoría: Explicación en comentarios de la diferencia Latch/FF. Código: Implementación comparativa de Latch D/JK/T frente a Flip-Flop D/JK/T. Control: Manejo correcto de señales asíncronas Preset y Clear.

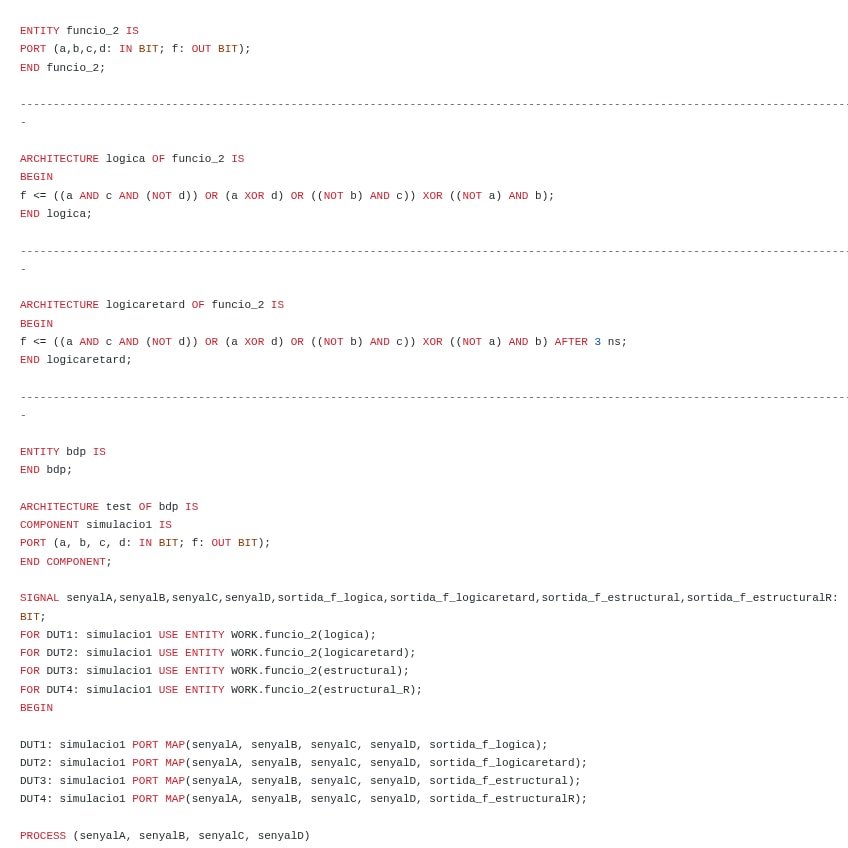

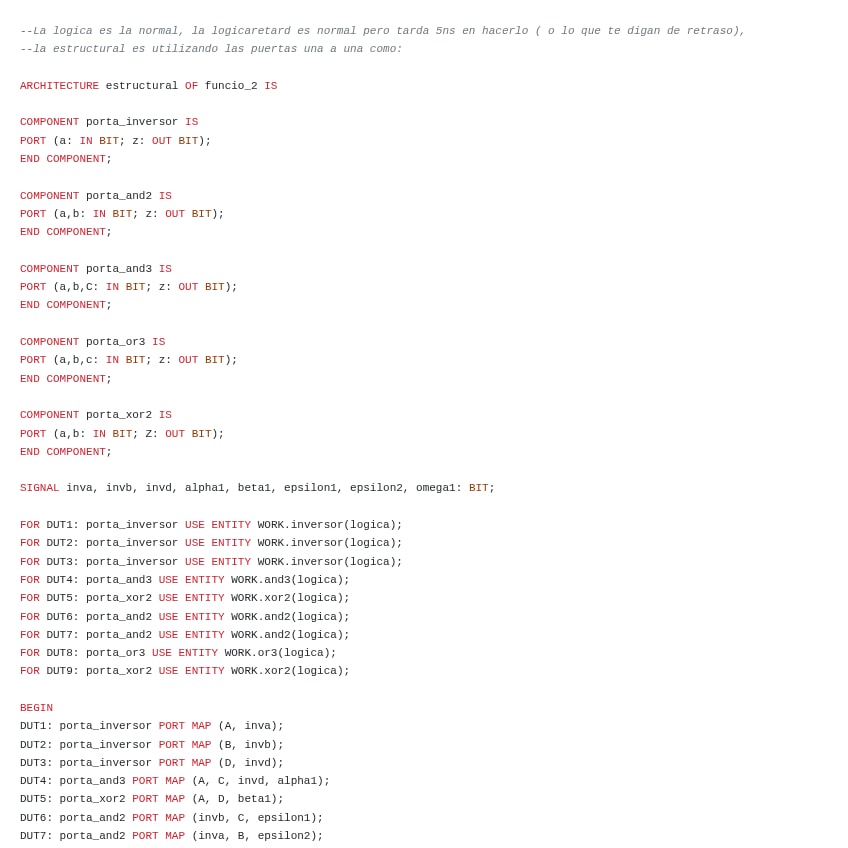

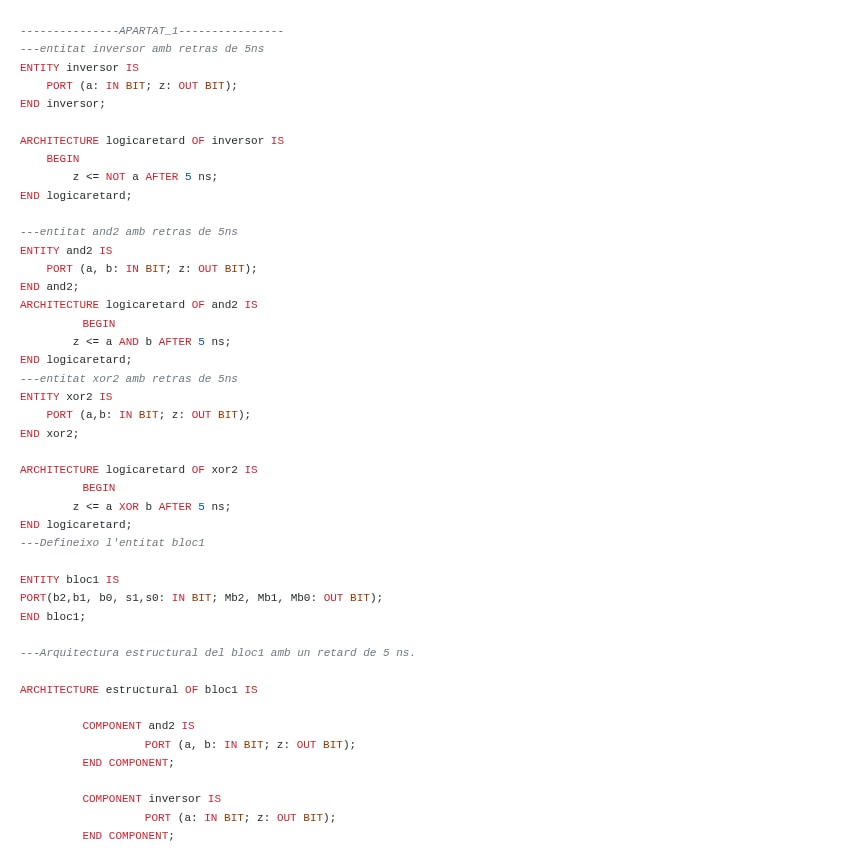

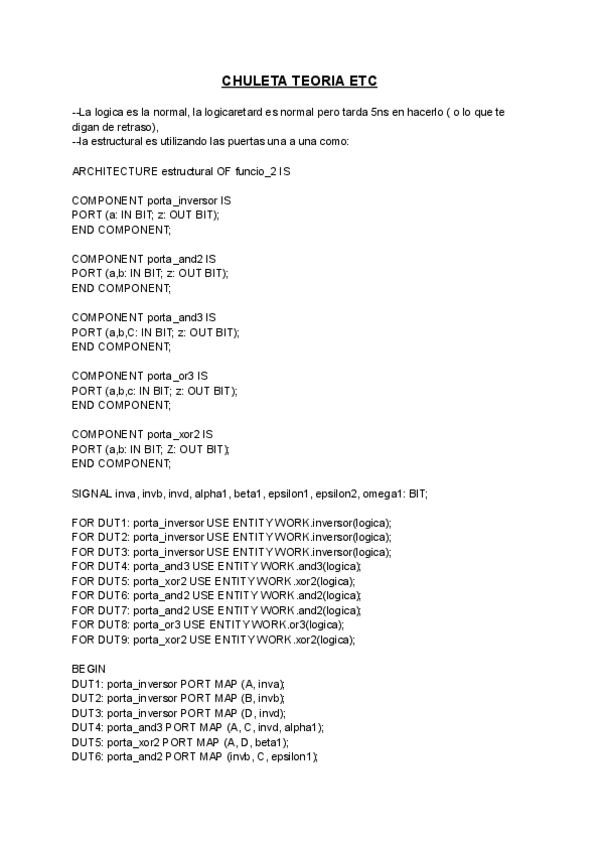

"Solución a la práctica de introducción a arquitecturas. Implementación de una función lógica compleja de 4 variables (a,b,c,d) comparando tres métodos: Lógica: Asignación directa. Lógica con Retardo: Uso de AFTER 3 ns. Estructural: Conexión de puertas

"Archivo 'Chuleta' esencial para copiar y pegar en cualquier práctica o examen. Contiene la sintaxis exacta (Entity + Architecture) de: Puertas: AND, OR, XOR, NAND (2, 3 y 4 entradas). Memorias: Latch D, Latch JK, Latch T. Flip-Flops: FF-D, FF-JK, FF-T

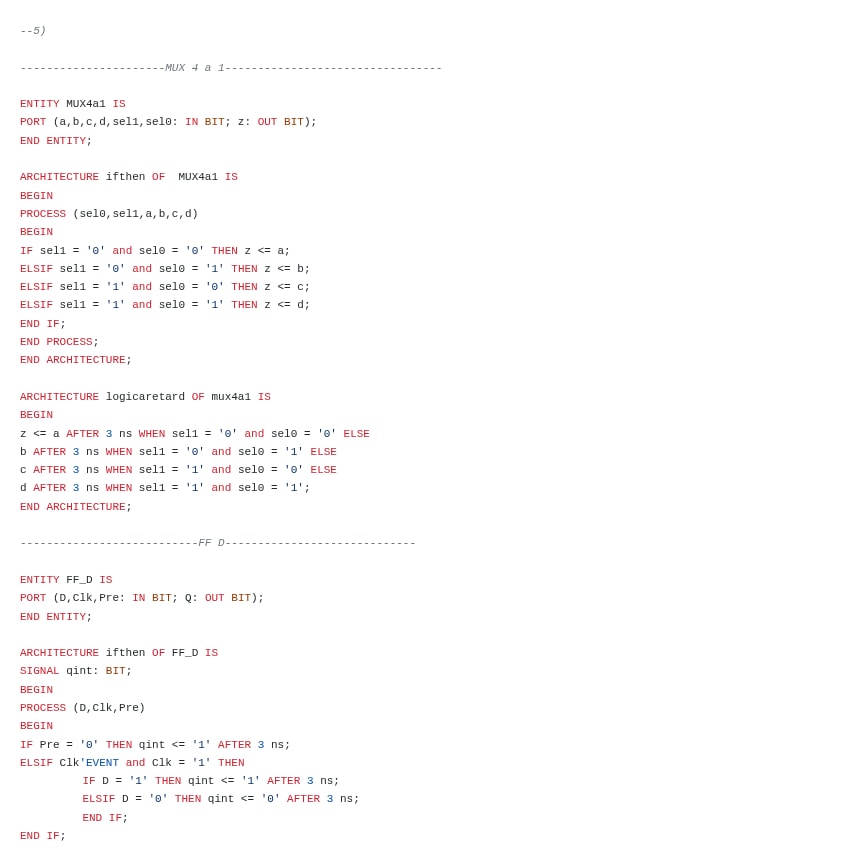

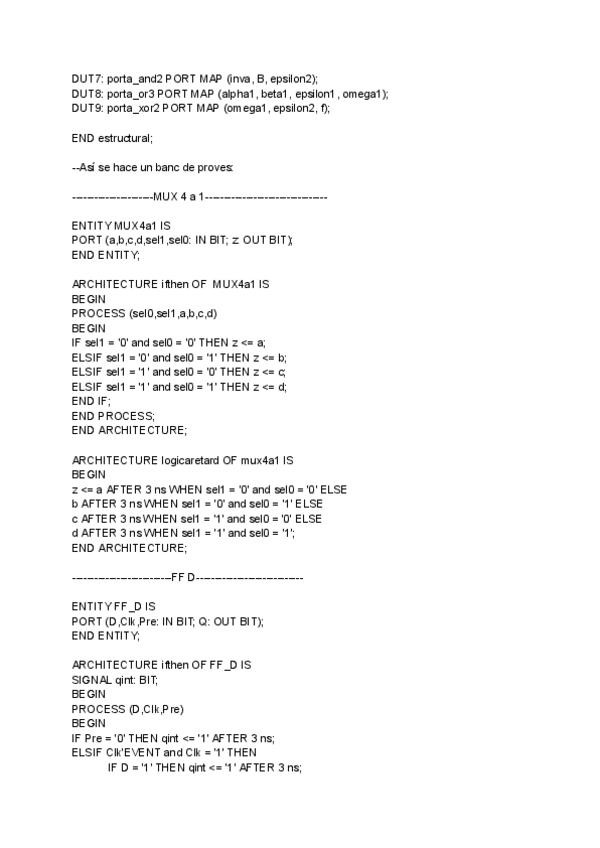

"Resumen práctico de teoría aplicada a VHDL. Muestra con ejemplos claros: Diferencia entre arquitectura logica, logicaretard y estructural. Cómo declarar Componentes y hacer Port Map. Cómo hacer un Multiplexor con IF-THEN-ELSE. Esqueleto básico de un

"Código VHDL para la primera parte de la práctica 5. Implementación de un circuito secuencial síncrono. Uso intensivo de Flip-Flops JK instanciados como componentes. Lógica de 'Próximo Estado' usando puertas XOR, AND e Inversores. Incluye test_p05d par

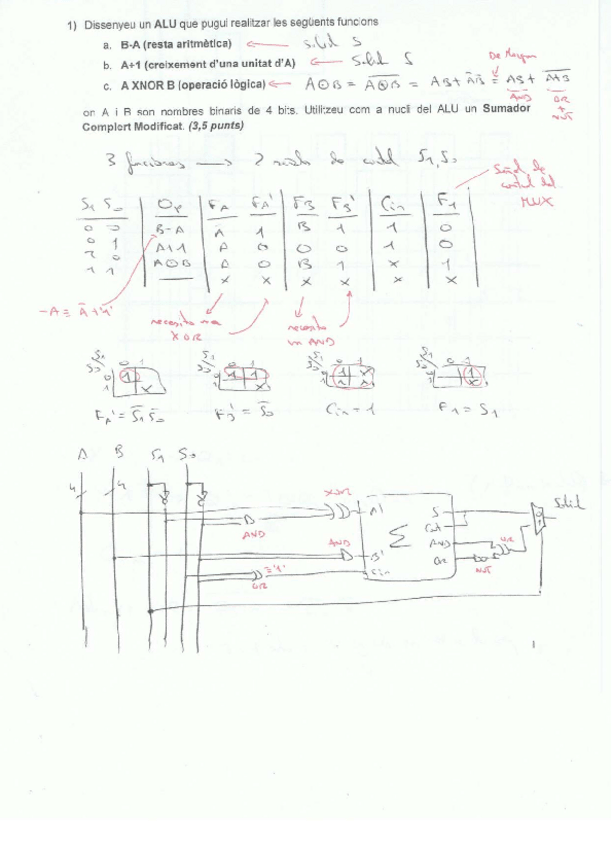

"El archivo más completo para aprobar la P5. Contiene la jerarquía completa: Sumador Completo (Full Adder): Implementación de Sum1Bit y Sum3Bits con carry. Registro de Desplazamiento: Código del Reg4Bits a partir de FFs de 1 bit. Bloque Lógico: Operaci

"Código VHDL resuelto de un circuito complejo que mezcla lógica combinacional y secuencial. Incluye: Uso simultáneo de Flip-Flop JK y Latch D con Preset y Clear. Arquitectura estructural con PORT MAP de componentes. Testbench (bdp) completo con generac

"Solución completa a la Práctica 4. Código funcionando que implementa: Multiplexor 4 a 1 con arquitectura comportamental (IF-THEN) y con retardos. Flip-Flop D sensible a flanco. Integración estructural conectando MUX y FF. Banco de pruebas para valida

La guía definitiva para sobrevivir a las prácticas y exámenes de DDB con ModelSim. No pierdas tiempo escribiendo código desde cero, aquí tienes las plantillas exactas (syntaxis perfecta) listas para usar. ¿Qué incluye este pack? Tipos de Arquitectura, C

apuntes

-

Apuntes

He publicado nuevos apuntes de 1º Disseny Digital Bàsic: Apuntes

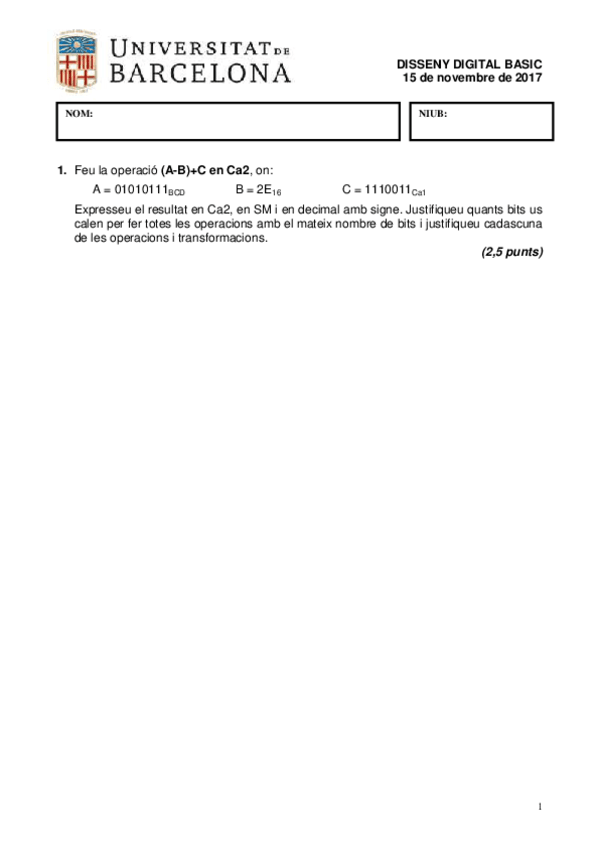

examenes

-

Examens

He publicado nuevos examenes de 1º Disseny Digital Bàsic: Examens

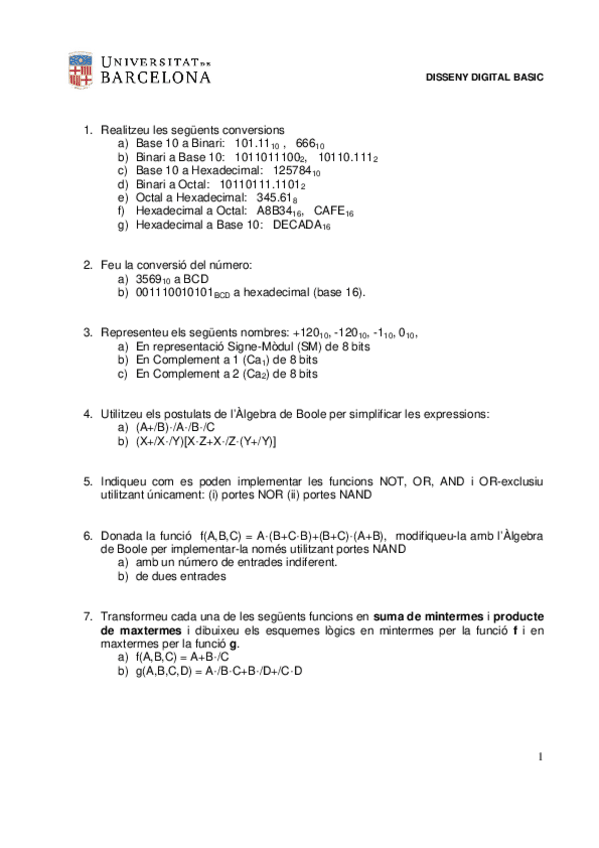

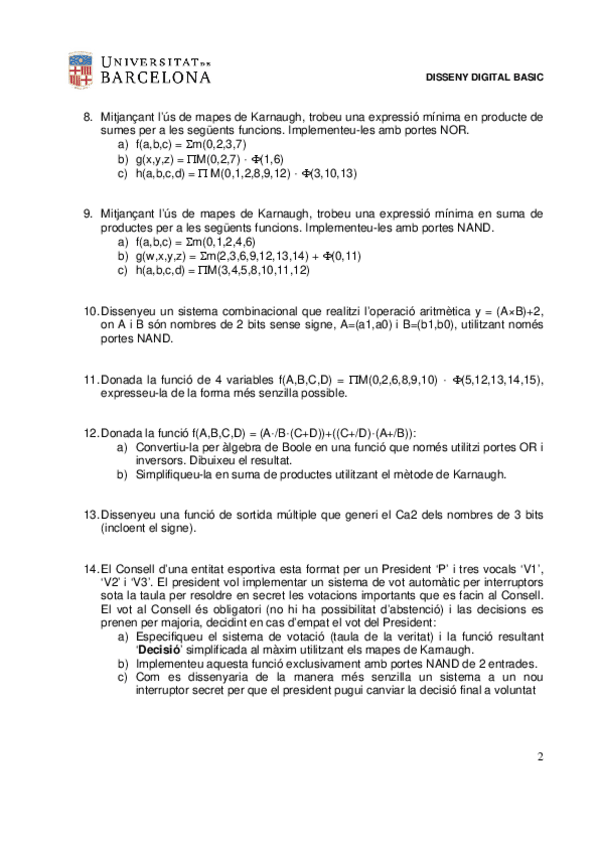

He publicado nuevos apuntes de 1º Disseny Digital Bàsic: Listado-de-Problemas-Enunciados-1.pdf

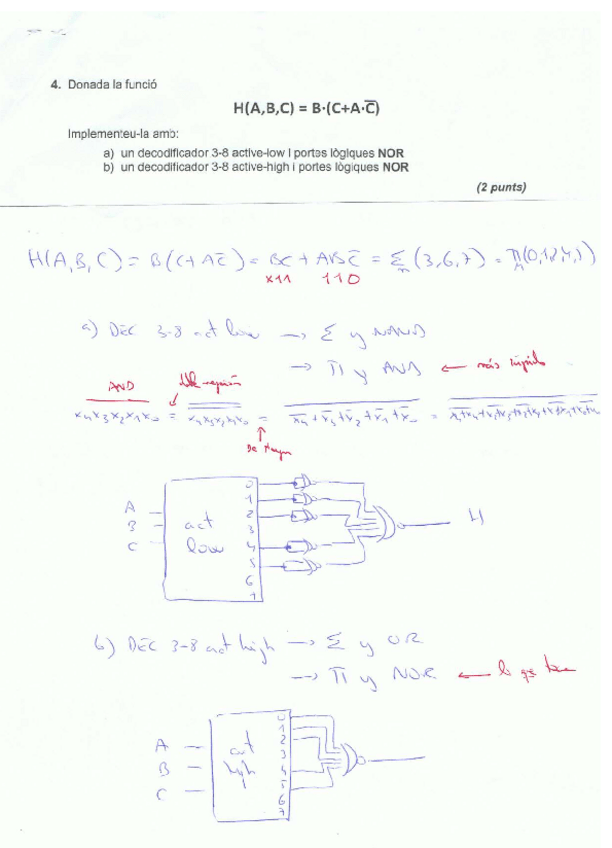

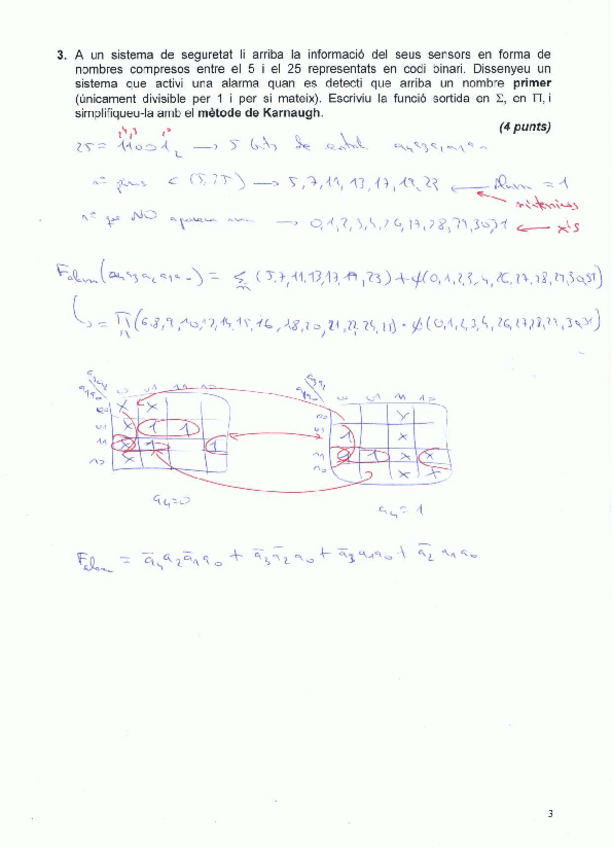

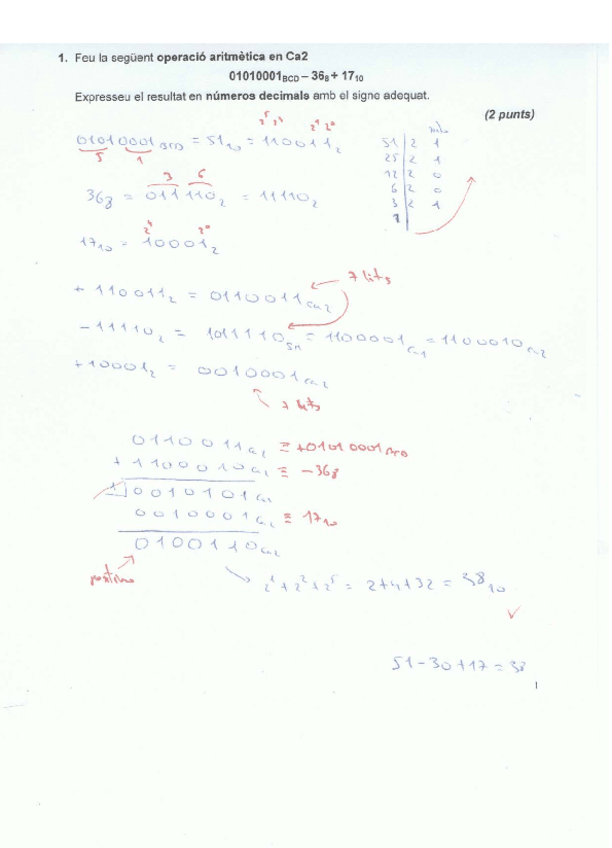

He publicado nuevos apuntes de 1º Disseny Digital Bàsic: ExamenParcial2014.pdf

¡Estás al día!

Has visto todos los archivos